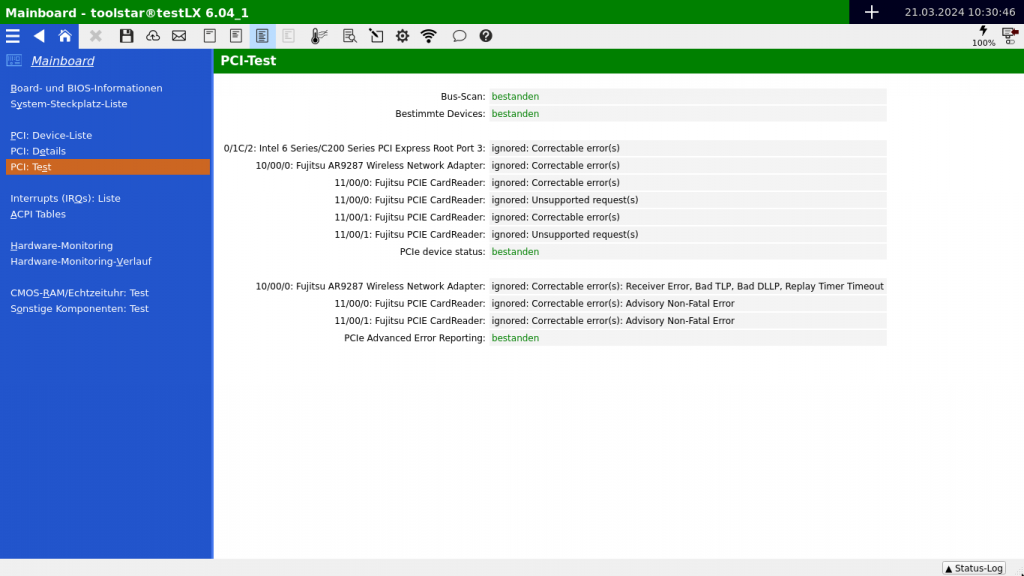

From version 6.05 onwards toolstar®testLX, toolstar®testWIN, toolstar®QuickCheckLX and toolstar®QuichCheckWIN new PCIe tests are available under the mainboard heading. The tests check the PCIe protocol for errors that have occurred in the communication between the CPU and the device or directly between the devices. It makes sense to insert this test at the beginning of a long-term test and at the end of a long-term test in order to be able to determine whether errors occurred before the test (which sometimes places a lot of strain on the device) and after the test.

What is being tested?

- Transaction Layer Errors

This is the upper layer where the packet is formed. The transaction layer checks are done end-to-end device, i.e. H. only by the requestor and the completer, and no checks are performed on the switch or bridge for the errors below.

– ECRC check failure

– Malformed TLP

– Completion Time-Outs

– Flow Control Protocol errors

– Unsupported Request

– Data corruption

– Completer abort

– Unexpected completion

– Receiver overflow - Data Link Layer Errors

This is the middle layer responsible for handling packet errors and responses. The following errors are checked at the DL level of Requester, Switch and Completer i.e. H. These errors are checked for requester, switch and completer.

– LCRC check failure for TLPs

– Sequence Number check

– LCRC check failures for DLLPs

– Replay Time-out

– Replay Number Rollover

– Data Link Layer Protocol errors - Physical Layer Errors

This is the third layer responsible for link training and transaction processing at the interface level. These errors are checked at the requester, switch and completer.

– Receiver error

– Link error

Evaluation of errors

It is important to know that you will always receive error output, even with correct systems. However, these outputs will be limited to Correctable errors, Non-Fatal errors and Unsupported requests errors. If you receive an uncorrectable error or a fatal error, an error will generally be thrown to alert you. In the output of the PCIe test, in addition to the exact cause of the error, you will also find the device to which the error relates.

Information about PCIe

Further information about PCIe and the individual layers as well as the structure of the protocol can be found here.

Further information about the motherboard tests

Further information can be found here in this Knowledgebase Article.